Code No:A109210203

### B.Tech II Year - I Semester Examinations, December 2011 ELECTRONIC DEVICES AND CIRCUITS (COMMON TO EEE, ECE, CSE, EIE, BME, IT, MCT, E.COMP.E, ETM, ICE) Time: 3 hours Max. Marks: 75

### Answer any five questions All questions carry equal marks

- 1.a) What is Fermi level? By indicating the position of Fermi level in intrinsic, n-type and p- type semiconductor, explain its significance in semiconductors?

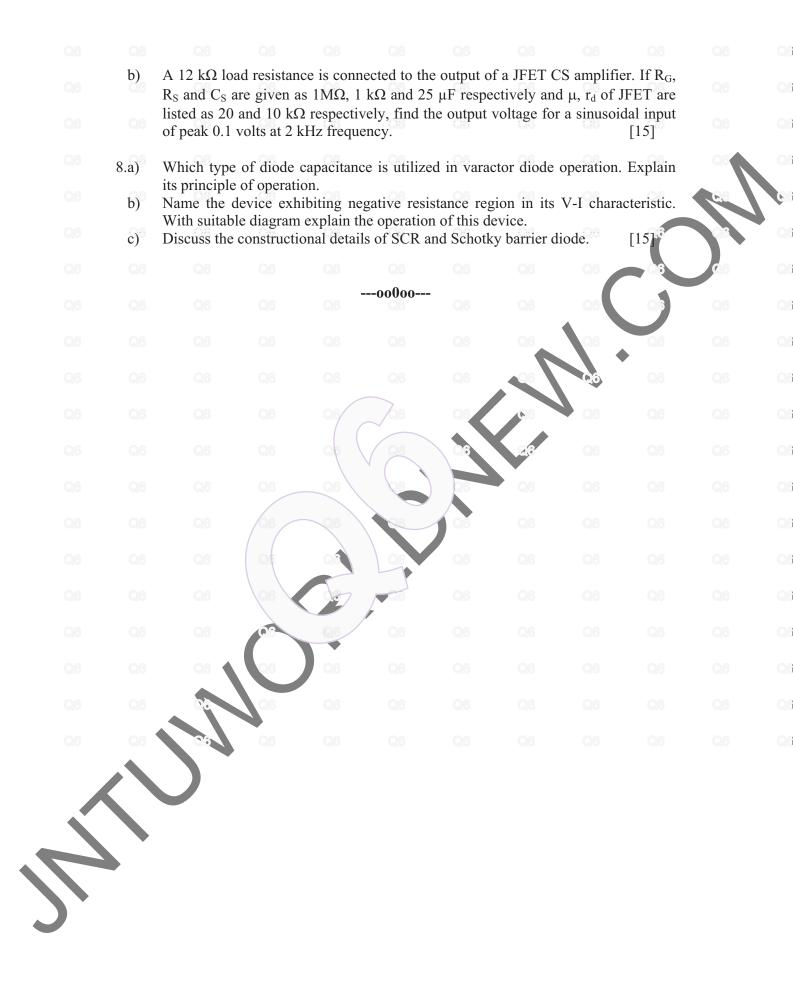

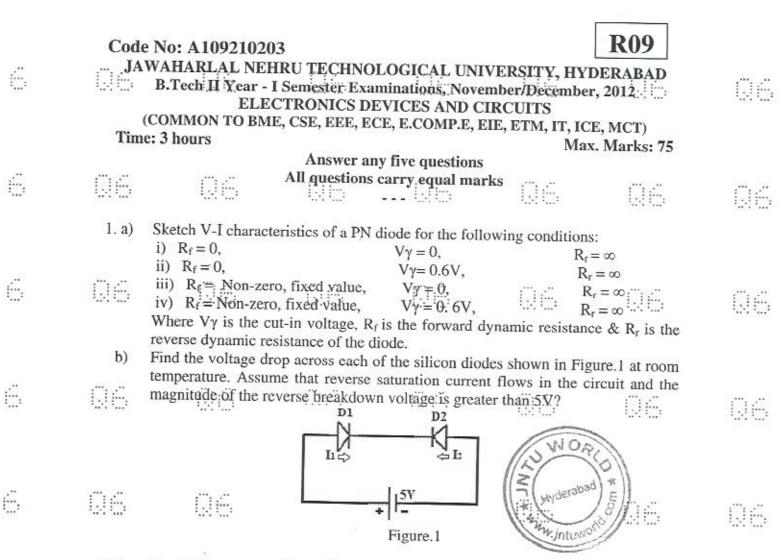

- b) Sketch V-I characteristics of a PN diode for the following conditions:

|       |                                | $\mathcal{O}$      |                                    |

|-------|--------------------------------|--------------------|------------------------------------|

| i)    | $R_{f} = 0$ ,                  | $V\gamma = 0$ ,    | $R_r = \infty$                     |

| ii)   | $R_{f}=0$ ,                    | $V\gamma = 0.6V$ , | $\mathbf{R}_{\mathrm{r}} = \infty$ |

| iii)  | $R_f =$ Non-zero, fixed value, | $V\gamma = 0$ ,    | $R_r = \infty$                     |

| iv)   | $R_f$ = Non-zero, fixed value, | $V\gamma = 0.6V,$  | $R_r = \infty$                     |

| Where | Vy is the cut-in voltage Reis  | the forward dynami | ic resistance & R is               |

Where  $V\gamma$  is the cut-in voltage,  $R_f$  is the forward dynamic resistance &  $R_r$  is the reverse dynamic resistance of the diode. [7+8]

- 2.a) Draw the block diagram of a regulated power supply and explain its operation.

- b) A full wave bridge rectifier having load resistance of  $100\Omega$  is fed with 220V, 50Hz through a step-down transformer of turns ratio 11:1. Assuming the diodes ideal, find

- i) DC output voltage

- ii) Peak inverse voltage

- iii) Rectifier efficiency.

- [9+6]

- 3.a) With a neat diagram explain the various current components in an NPN bipolar junction transistor & hence derive general equation for collector current, I<sub>C</sub>?

- b) What is Early-effect; explain why it is called as base-width modulation? Discuss its consequences in transistors in detail? [9+6]

- 4.a) What is 'Thermal Runaway' in transistors? Derive the condition to prevent 'Thermal Runaway' in Bipolar Junction Transistors.

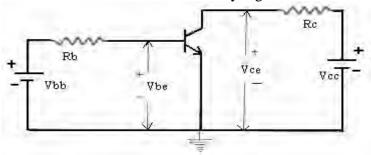

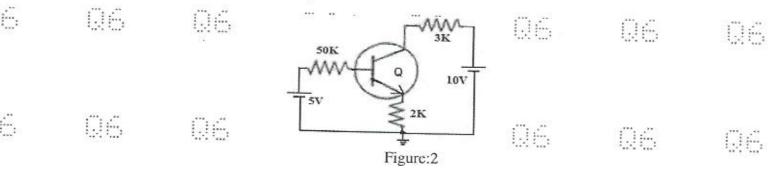

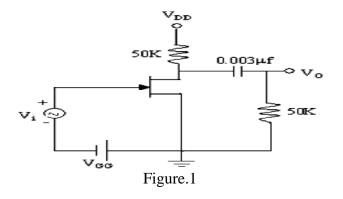

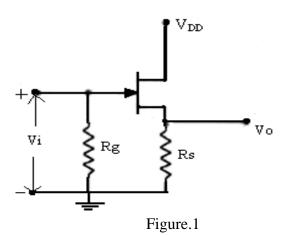

- b) A silicon NPN transistor has Ico = 20nA and  $\beta$ =150, V<sub>be</sub> = 0.7V. It is operated in Common Emitter configuration (as shown in Figure.1) having Vbb = 4.5V,R<sub>b</sub>= 150K,R<sub>c</sub> = 3K, V<sub>cc</sub> = 12V. Find the emitter, base and collector currents and also verify in which region does the transistor operate. What will happen if the value of the collector resistance is increased to very high values? [5+10]

Figure.1

- 5.a) Draw the circuit diagram & small signal equivalent of CB amplifier using accurate h-parameter model. Derive expressions for A<sub>V</sub>, A<sub>I</sub>, R<sub>i</sub> and R<sub>0</sub>.

- b) Draw small signal equivalent circuit of Emitter Follower using accurate hparameter model. For the emitter follower circuit with  $R_S = 0.5K$  and  $R_L = 5K$ , calculate  $R_i$ ,  $A_V$  and  $R_O$ . Assume,  $h_{fe} = 50$ ,  $h_{ie} = 1K$ ,  $h_{oe} = 25 \ \mu A/V$ . [8+7]

- 6.a) Explain the construction & operation of a P-channel MOSFET in enhancement and depletion modes with the help of static drain characteristics and transfer characteristics?

- b) "A depletion mode MOSFET can also be operated in enhancement mode but an enhancement mode MOSFET cannot be operated in depletion mode". Justify?

[10+5]

- 7.a) Explain the need of biasing a Field Effect Transistor. With necessary equations and valid reasons explain why a simple 'fixed bias' arrangement for FETs is not used in practical applications?

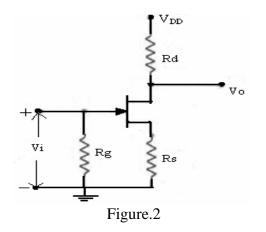

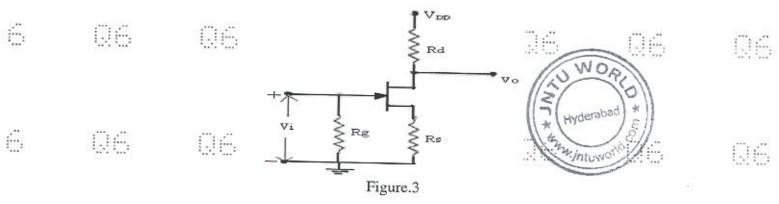

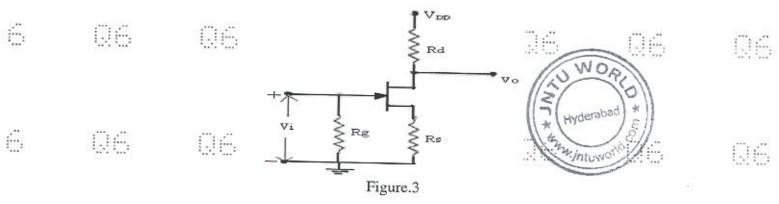

- b) A Common Source FET amplifier circuit shown in Figure.2 with un-bypassed  $R_s$  has the following circuit parameters:  $R_d = 15K$ ,  $R_s = 0.5K$ , Rg = 1M,  $r_d = 5K$ ,  $g_m = 5mS$  and  $V_{DD} = 20$  V. Calculate  $A_V$ ,  $A_I$ ,  $R_i$  and  $R_0$ . [7+8]

- 8.a) With neat energy band diagrams, explain the V-I characteristics of Tunnel diode. Also discuss the negative resistance property of tunnel diode.

- b) With neat sketches explain the operation of Schottky Barrier Diode. [10+5]

\*\*\*\*\*\*

Code No:A109210203

SET-2

### B.Tech II Year - I Semester Examinations, December 2011 ELECTRONIC DEVICES AND CIRCUITS (COMMON TO EEE, ECE, CSE, EIE, BME, IT, MCT, E.COMP.E, ETM, ICE) Time: 3 hours Max. Marks: 75

### Answer any five questions All questions carry equal marks

- 1.a) What do you understand about the depletion region at a PN junction, with the help of necessary diagrams and derive expression for barrier potential.

- b) Derive the expression for transition capacitance,  $C_T$  of a PN diode. [9+6]

- 2.a) With neat sketches explain the operation of a FWR with L- section filter & derive the expression for its ripple factor. Also explain the necessity of a bleeder resistor in a practical L- section filter.

- b) Determine the ripple factor of an L-section filter comprising a 10H choke and 8μF capacitor, used with a FWR. The DC voltage at the load is 50V. Assume the line frequency as 50Hz. [10+5]

- 3.a) Draw the circuit diagram of NPN transistor in Common Emitter(CE) configuration. With neat sketches and necessary equations, describe its static input-output characteristics and clearly indicate the cut-off, saturation & active regions on the output characteristics?

- b) Calculate the values of  $I_C$  and  $I_E$  for a transistor with  $\alpha_{dc} = 0.99$  and  $I_{CBO} = 5\mu A$ , if  $I_B$  is measured as 20  $\mu A$ . [10+5]

- 4.a) What do you mean by biasing a transistor? Explain the need of biasing a transistor for the construction of a faithful amplifier?

- b) Design a collector to base bias circuit using silicon transistor to achieve a stability factor of 20, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4 \text{ mA } \& \beta = 50$ . [7+8]

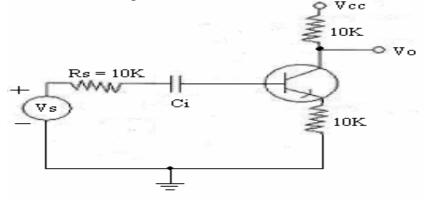

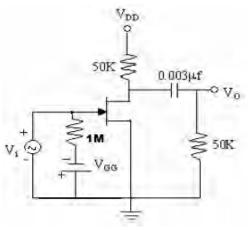

- 5.a) In the amplifier circuit shown in Figure.1, estimate input resistance and voltage gain? Also derive the expressions used?

Figure.1

b) Compare CB, CE and CC amplifiers with respect to  $A_V$ ,  $A_I$ ,  $R_I \& R_O$ ? [10+5]

- 6.a) Explain the construction & operation of a P-channel MOSFET in enhancement and depletion modes with the help of static drain characteristics and transfer characteristics?

- b) In an n-channel FET, the effective channel width is  $3 \times 10^{-4}$  cm and the donor impurity concentration is  $10^{15}$  electrons/cm<sup>3</sup>. Find the pinch-off voltage? [10+5]

- 7.a) Draw the basic circuit and small-signal model of Common Drain FET amplifier. Derive expressions for voltage gain and output resistance?

- b) Compare the merits & demerits of a Bipolar Junction Transistor (BJT) with Field effect Transistor (FET) in detail? [8+7]

- 8.a) Draw the firing characteristics of SCR and briefly explain it.

- b) Define the following with respect to SCR

- i) Forward break over voltage

- ii) Reverse break over voltage

- iii) Holding current

- iv) Gate trigger current.

[7+8]

\*\*\*\*\*\*

Code No:A109210203

[9+6]

#### B.Tech II Year - I Semester Examinations, December 2011 ELECTRONIC DEVICES AND CIRCUITS (COMMON TO EEE, ECE, CSE, EIE, BME, IT, MCT, E.COMP.E, ETM, ICE) Time: 3 hours Max. Marks: 75

# Answer any five questions All questions carry equal marks

- 1.a) With the help of necessary sketches explain the potential distribution in an open circuited PN junction.

- b) With the help of V-I Characteristics, explain the operation of a PN Diode under Forward bias and Reverse bias. [7+8]

- 2.a) With neat sketches explain the operation of a FWR with shunt capacitor filter & Derive the expression for its ripple factor.

- b) A bridge rectifier uses four identical diodes having forward resistance of  $5\Omega$  each. Transformer secondary resistance is 5 ohms and the secondary voltage is 30V (rms). Determine the dc output voltage for  $I_{dc} = 200$  mA and value of the output ripple voltage. [7+8]

- 3.a) Draw the circuit diagram of NPN transistor in Common Base (CB) configuration. With neat sketches and necessary equations, describe its static input- output characteristics and clearly indicate the cut-off, saturation & active regions on the output characteristics?

- b) With reference to a BJT, define the following terms and explain:

i) Emitter efficiency.

ii) Base transportation factor.

iii) Large signal current gain.

- 4.a) Obtain the condition for thermal stability of a BJT used in a biasing circuit?

- b) Design a self bias circuit using silicon transistor to achieve a stability factor of 10, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [5+10]

- 5.a) Draw the circuit diagram & small signal equivalent circuit of CE amplifier using accurate h-parameter model. Derive expressions for A<sub>V</sub>, A<sub>I</sub>, R<sub>i</sub> & R<sub>0</sub>.

- b) A bipolar junction transistor with  $h_{ie} = 1100\Omega$ ,  $h_{fe} = 50$ ,  $h_{re} = 2.4 \times 10^{-4}$ ,  $h_{oe} = 25 \mu A/V$ , is to drive a load of 1K $\Omega$  in Emitter-Follower arrangement. Estimate  $A_V$ ,  $A_I$ ,  $R_i \& R_0$ ? [8+7]

- 6.a) With the help of neat sketches and characteristic curves explain the construction & operation of a JFET and mark the regions of operation on the characteristics?

- b) Show that in Field Effect Transistor, the transconductance,  $g_m = g_{mo} [1 V_{GS}/Vp]$ [8+7]

- 7.a) Draw the basic structure and equivalent circuit of UJT. Explain how the UJT can be used as a negative-resistance device with the aid of static characteristics.

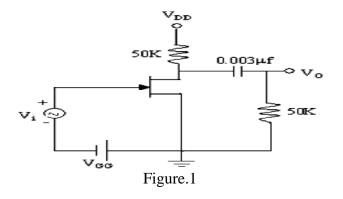

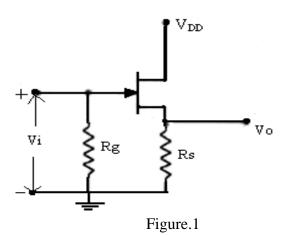

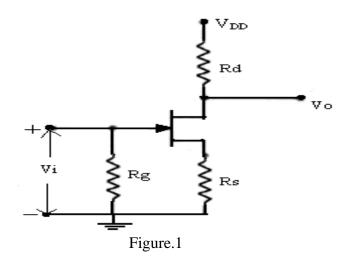

- b) In the common source FET amplifier shown in Figure.1, the transconductance and drain dynamic resistance of the FET are 5mA/V and  $1M\Omega$  respectively. Estimate  $A_V$ ,  $R_i \& R_0$ ?

Figure.1

- 8.a) With neat sketches and necessary expressions describe V-I characteristics of a semiconductor photo diode?

- b) With neat sketches and necessary expressions describe the operation of Varactor diode? [8+7]

\*\*\*\*\*\*\*

Code No:A109210203

#### B.Tech II Year - I Semester Examinations, December 2011 ELECTRONIC DEVICES AND CIRCUITS (COMMON TO EEE, ECE, CSE, EIE, BME, IT, MCT, E.COMP.E, ETM, ICE) Time: 3 hours Max. Marks: 75 Answer any five questions

# All questions carry equal marks

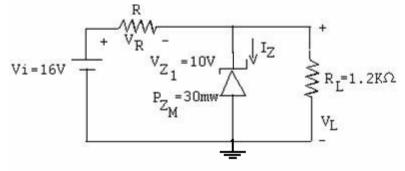

- 1.a) Explain Avalanche and Zener break down mechanisms in semiconductors and compare them?

- b) For the Zener diode circuit shown in Figure 1, determine  $V_L$ ,  $V_R$ ,  $I_Z$  & R. [5+10]

Figure.1

- 2.a) With reference to the Rectifiers, Explain the following terms:

i) Ripple Factor

ii) Efficiency

iii) Peak Inverse Voltage (PIV)

iv) % Regulation

- b) A 230 V, 60Hz voltage is applied to the primary of a 5:1 step down, center tapped transformer used in a full wave rectifier having a load of 900 $\Omega$ . If the diode resistance and the secondary coil resistance together have a resistance of 100  $\Omega$ , determine

- i) DC voltage across the load.

- ii) DC current flowing through the load.

- iii) DC power delivered to the load.

- iv) PIV across each diode.

[8+7]

- 3.a) Draw the circuit diagram of NPN transistor in Common Collector (CC) configuration. With neat sketches and necessary equations, describe its static input- output characteristics and clearly indicate the cut-off, saturation & active regions on the output characteristics?

- b) Derive the relationship among  $\alpha$ ,  $\beta$  and  $\gamma$  in transistors? [9+6]

- 4.a) What do you mean by biasing a transistor? Explain the need of biasing a transistor for the construction of a faithful amplifier?

- b) Design an Emitter bias circuit using silicon transistor to achieve a stability factor of 20, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4 \text{ mA } \& \beta = 50$ . [7+8]

- 5.a) Draw the circuit and small-signal model of CE amplifier with unbypassed emitter resistor. Derive the expressions for input resistance & voltage gain?

- b) A bipolar junction transistor with  $h_{ie} = 1100\Omega$ ,  $h_{fe} = 50$ ,  $h_{re} = 2.4 \times 10^{-4}$ ,  $h_{oe} = 25 \mu A/V$ , is to drive a load of 1K $\Omega$  in CB amplifier arrangement. Estimate  $A_V$ ,  $A_I$ ,  $R_i \& R_0$ . [8+7]

- 6.a) Explain the construction & operation of a N-channel MOSFET in enhancement and depletion modes with the help of static drain characteristics and transfer characteristics?

- b) In an n-channel FET, the effective channel width is  $3 \times 10^{-4}$  cm and the donor impurity concentration is  $10^{15}$  electrons/cm<sup>3</sup>. Find the pinch-off voltage? [10+5]

- 7.a) Show the self-bias arrangement for a Field Effect Transistor. With necessary expressions describe the procedure of Q-point establishment and stabilization?

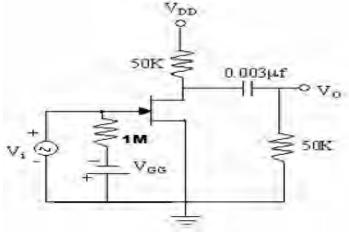

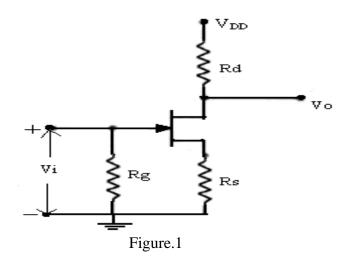

- b) In the common source FET amplifier shown in Figure.2, the transconductance and drain dynamic resistance of the FET are 5mA/V and  $1M\Omega$  respectively. Estimate  $A_V$ ,  $R_i \& R_0$ . [8+7]

Figure.2

- 8.a) With neat energy band diagrams, explain the V-I characteristics of Tunnel diode. Also discuss the negative resistance property of tunnel diode.

- b) Draw the two-transistor model of SCR and explain its operation. [10+5]

\*\*\*\*\*\*\*

www.jntuworld.com // www.android.jntuworld.com // www.jwjobs.net // www.android.jwjobs.net

|   |       |                                     |             |             |              |                             |             |          |                        |              | Q      |

|---|-------|-------------------------------------|-------------|-------------|--------------|-----------------------------|-------------|----------|------------------------|--------------|--------|

|   |       |                                     |             |             |              |                             |             | Q6       | <b>R09</b>             |              | Q6     |

|   |       | No: 09A3030                         |             |             |              |                             |             | L        |                        |              |        |

|   | JA    | WAHARLA<br>B.Te                     |             |             |              | CAL UNIVI<br>inations, Ma   | ,           |          | RABAD                  |              | Qß     |

|   |       |                                     |             |             |              | erial Science<br>, MIM, AMH |             |          |                        | QG           | QB     |

|   | Time: | : 3 hours                           | 06          |             | 06           | O6                          |             | Max. I   | Marks: 75              | <b>A B B</b> | Gr     |

|   |       |                                     |             | Answer      | any five q   | uestions                    |             |          |                        |              |        |

|   |       |                                     | Q6 A        |             | •            | qual marks                  | Q6          |          | 96                     | 03           | Q      |

|   |       |                                     |             |             |              |                             |             |          | 66                     | <b>0</b> 6   | Q6     |

|   | 1.a)  | Describe an                         |             |             |              |                             |             |          |                        |              |        |

|   | b)    | How does g<br>any two met           |             |             |              |                             | rties of ma | aterials | P Describe<br>[15]     |              | Q6     |

|   | Q6    | Qß                                  | 03          | Q6          | 06           | Q6                          | Q6          | Q6       | Q6                     |              | Q      |

|   | 2.a)  | What are the                        |             |             |              | *                           |             |          | •<br>[1 ]]             |              |        |

|   | b)    | Discuss abo                         | ut the vari | ious types  | of electron  | 1 compounds                 | S. 💦        | Q6       | [15]                   |              | Qß     |

|   | 3.a)  | Differentiat                        |             |             |              | 08                          | 66          | 06       |                        |              | Q6     |

|   |       | i) Eutectic a                       |             |             | ormation     |                             |             |          |                        |              |        |

|   |       | ii) Peritectic                      |             |             | 06           | 6                           | 28          |          |                        |              | Q6     |

|   | b)    | What is Gib                         | b's phase   | rule? Expl  | lain its imp | portance.                   |             |          | [15]                   |              |        |

|   |       |                                     |             | 06          | 06           |                             | O6          |          |                        |              | Qð     |

|   | 4.a)  | What are the                        |             |             |              |                             |             |          |                        |              |        |

|   | b)    | List out the                        |             |             |              |                             |             |          |                        |              | Q6     |

|   | c)    | What are the                        | e propertie | es and appl | lications of | f tool steels?              | ?           |          | [15]                   |              | - Cito |

|   |       |                                     |             |             |              | 08                          |             |          |                        |              | 08     |

|   | 5.a)  | Indicate the                        | e temperat  | ture range  | of the fo    | llowing hea                 | t treatmer  | nts on   | Fe – Fe <sub>3</sub> C |              | Giù    |

|   |       | equilibrium                         | diagram     | (i) Annea   | ling (ii) N  | Vormalizing                 | (iii) Ha    | ardenin  | g                      |              | 00     |

|   |       | (iv) Temper                         |             |             | 100          |                             |             |          | <b>8</b> Q6            |              | Q6     |

|   | b)    | Distinguish                         | between I   | nduction H  | Hardening    | and Flame h                 | nardening.  |          | [15]                   |              |        |

|   | U.O   | 610                                 | 0.0         |             | U0 0         |                             | 40          |          | - 00                   |              | Q6     |

|   | 6.    | Describe the                        | e structure | and prope   | erties of    |                             |             |          |                        |              |        |

|   |       | a) Duralumi                         |             | Ct6 1       |              |                             |             |          |                        |              | Q6     |

|   |       | b) (α +β)Ti                         |             |             |              |                             |             |          |                        |              |        |

|   |       | c) Aluminiu                         |             | s Q6        | Q6           |                             |             |          |                        |              | Q6     |

|   |       | d) Muntz m                          |             |             |              |                             |             |          | [15]                   |              |        |

|   |       | 05                                  | Q6          |             |              |                             |             |          | Q6                     |              | Q6     |

|   | 7.a)  | Define cerat                        | mics. Clas  | sify them.  | Give som     | e important                 | application | ns of ce | eramics.               |              |        |

|   | b)    | Discuss abo                         |             | •           |              | r                           | rr #0101    |          | [15]                   |              |        |

|   | 8.    | Write short                         | notes on t  | he followi  | ng:          |                             |             |          |                        |              |        |

|   |       | a) Metal ma                         |             |             | 0            |                             |             |          |                        |              |        |

|   |       | b) Nano ma                          |             |             |              |                             |             |          |                        |              |        |

|   |       | c) Cryogeni                         |             | nt.         |              |                             |             |          | [15]                   |              |        |

|   |       | -, - <u>,</u> - <u>,</u> - <u>,</u> |             | -           |              |                             |             |          | L-~]                   |              |        |

| Ì |       |                                     |             |             | -            |                             |             |          |                        |              |        |

|   |       |                                     |             |             | 0000         | 00                          |             |          |                        |              |        |

| Code No:A109210203   |   |

|----------------------|---|

| Couc 110./110/210205 | L |

Max. Marks: 75

### B.Tech II Year I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

# Time: 3 hours

#### Answer any five questions All questions carry equal marks

- 1.a) Explain the concept of diode capacitance. Derive expression for transition capacitance?

- b) Find the value of D.C. resistance and A.C resistance of a Germanium junction diode at  $25^{\circ}$  C with reverse saturation current,  $I_{o} = 25\mu$ A and at an applied voltage of 0.2V across the diode. [8+7]

- Define the following terms and derive the equations with respect to half-wave rectifier:

i) Ripple factor

ii) Rectification efficiency

iv) % Regulation.

- 3.a) With neat sketches and necessary waveforms, explain the input and output characteristics of a BJT in CB configuration. Also derive expression for output current.

- b) Derive the relation among  $\alpha$ ,  $\beta$  and  $\gamma$ .

- 4.a) Explain the basic requirements of transistor biasing. Verify these requirements in collector to base bias circuit.

- b) Design a fixed bias circuit using silicon transistor, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [8+7]

- Draw the circuit diagram, AC equivalent & small signal equivalent of Common Base amplifier using accurate h-parameter model. Derive expressions for A<sub>Vs</sub>, A<sub>Is</sub>, R<sub>I</sub> & R<sub>0</sub>. [15]

- 6.a) Explain the construction & operation of an N-channel enhancement and depletion MOSFET with the help of static drain characteristics and transfer characteristics.

- b) Define pinch-off voltage and transconductance in field effect transistors. [12+3]

- 7.a) Draw the small-signal model of common drain FET amplifier. Derive expressions for voltage gain and output resistance.

- b) Calculate voltage gain  $A_V = V_O/V_i$  and  $R_O$  at 1KHz for the circuit shown in Figure 1. FET parameters are gm=2mA/V and rd =10k. Neglect capacitances.

[8+7]

[10+5]

8. With neat energy band diagrams, explain the V-I characteristics of Tunnel diode in detail. Also explain the negative-resistance region in the characteristics and applications of Tunnel diode. [15]

# B.Tech II Year - I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

### Time: 3 hours

Max. Marks: 75

#### Answer any five questions All questions carry equal marks

- 1.a) What do you understand by depletion region at p-n junction? What is the effect of forward and reverse biasing of p-n junction on the depletion region? Explain with necessary diagrams.

- b) Explain Zener and avalanche breakdown mechanisms in detail. [8+7]

- 2.a) Draw the circuit diagram of full-wave rectifier with inductor filter. Explain its operation with necessary equations.

- b) A HWR circuit supplies 100mA DC current to a  $250\Omega$  load. Find the DC output voltage, PIV rating of a diode and the r.m.s. voltage for the transformer supplying the rectifier. [8+7]

- 3.a) With neat sketches and necessary waveforms, explain the input and output characteristics of a BJT in CE configuration. Also derive expression for output current.

- b) Calculate the collector current and emitter current for a transistor with  $\alpha = 0.99$ and  $I_{CBO} = 50\mu A$  when the base current is 20 $\mu A$ . [10+5]

- 4.a) What is thermal runaway in transistors? Obtain the condition for thermal stability in transistors.

- b) Design a self bias circuit using silicon transistor to achieve a stability factor of 10, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [6+9]

- Draw the circuit diagram, AC equivalent & small signal equivalent of Emitter Follower amplifier using accurate h-parameter model. Derive expressions for A<sub>Vs</sub>, A<sub>Is</sub>, R<sub>I</sub> & R<sub>0</sub>. [15]

- 6.a) With the help of neat sketches and characteristic curves explain the construction & operation of a JFET and mark the regions of operation on the characteristics.

- b) Derive expression for transconductance in a field effect transistor. [10+5]

- 7.a) Draw the small-signal model of common source FET amplifier. Derive expressions for voltage gain and output resistance.

- b) Give the UJT symbol and simplified equivalent circuit with external resistors included. Describe its negative-resistance nature, with the help of V-I characteristics. [7+8]

- 8.a) With neat sketches, explain the principle of operation of Schottky Barrier Diode.

- b) With neat sketches, explain V-I characteristics of semiconductor Photo Diode.

[8+7]

\*\*\*\*\*\*\*

Max. Marks: 75

# B.Tech II Year - I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

# Time: 3 hours

#### Answer any five questions All questions carry equal marks

- 1.a) Explain about various current components in a forward biased p-n junction diode.

- b) With neat sketches and necessary waveforms explain about the regulation characteristics of Zener diode. [7+8]

- 2.a) Draw the circuit of full-wave rectifier with capacitor filter. Explain its operation with necessary equations.

- b) A full wave rectifier circuit uses two silicon diodes with a forward resistance of  $20\Omega$  each. A DC voltmeter connected across the load of  $1K\Omega$  reads 55.4 volts. Calculate

| i) I <sub>rms</sub> | ii) Average voltage across each diode     |       |

|---------------------|-------------------------------------------|-------|

| iii) ripple factor  | iv) Transformer secondary voltage rating. | [7+8] |

- 3.a) With neat sketches and necessary waveforms, explain the input and output characteristics of a BJT in CE configuration. Also derive expression for output current.

- b) The reverse leakage current of the transistor when connected in CB configuration is 0.2  $\mu$ A while it is 18  $\mu$ A when the same transistor is connected in CE configuration. Calculate  $\alpha$  and  $\beta$  of the transistor. [10+5]

- 4.a) Explain how I<sub>CO</sub> variations are compensated with the help of diode and thermistor in transistor biasing circuits?

- b) Design a collector to base bias circuit using silicon transistor to achieve a stability factor of 20, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [7+8]

- 5. Draw the basic circuit, ac equivalent and h-parameter model of a Common Emitter amplifier. Derive expressions for  $A_{Vs}$ ,  $A_{Is}$ ,  $R_I \& R_O$ . [15]

- 6.a) Explain the construction & operation of an P-channel enhancement and depletion MOSFET with the help of static drain characteristics and transfer characteristics.

- b) Explain why field effect transistor is called as unipolar and voltage controlled device. [12+3]

- 7.a) Draw the small-signal model of common gate FET amplifier. Derive expressions for voltage gain and input resistance.

- b) A Common Source FET amplifier circuit shown in Figure.1 with unbypassed  $R_s$  has the following circuit parameters:  $R_d = 15K$ ,  $R_S = 0.5K$ , Rg = 1M,  $r_d = 5K$ ,  $g_m = 5mS$  and  $V_{DD} = 20$  V. Calculate  $A_V \& R_O$ . [8+7]

8. With neat energy band diagrams, explain the V-I characteristics of Tunnel diode in detail. Also explain the negative-resistance region in the characteristics. [15]

| Code No:A109210203 |  |

|--------------------|--|

| COUE NO.A109210203 |  |

#### B.Tech II Year - I Semester Examinations, May-June, 2012 **ELECTRONIC DEVICES AND CIRCUITS**

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

**Time: 3 hours**

Max. Marks: 75

[8+4+3]

#### Answer any five questions All questions carry equal marks

- With neat sketches and necessary waveforms explain the volt ampere 1.a)characteristics of PN diode.

- Explain the temperature dependence of VI characteristics of PN diode. b)

- Compare ideal and practical diodes. c)

- 2.a) Draw the circuit of full-wave rectifier with L-section filter and derive expression for its ripple factor.

- A 230 V, 60Hz voltage is applied to the primary of a 5:1 step down, center tapped b) transformer used in a full wave rectifier having a load of 900 $\Omega$ . If the diode resistance and the secondary coil resistance together has a resistance of  $100\Omega$ , determine

i) dc voltage across the load. iii) dc power delivered to the load.

- ii) dc current flowing through the load. [7+8]

- iv) PIV across each diode.

- With the help of a neat diagram explain different current components in an NPN 3.a) bipolar junction transistor.

- With reference to bipolar junction transistors, define the following terms and b) explain.

i) Emitter efficiency.

ii) Base Transportation factor.

iii) Large signal current gain.

[9+6]

- Explain the basic requirements of transistor biasing. Verify these requirements in 4.a) Emitter feedback bias circuit.

- An NPN Silicon transistor with  $\beta$ =50 is used in a common emitter circuit with b)  $V_{CC}=10V$ ,  $R_{C}=2K$ . The bias is obtained by connecting a 100K resistance from collector to base. Find ii) Stability factor, S i) Q-Point [8+7]

- 5.a) Compare CB, CE and CC amplifiers in view of A<sub>V</sub>, A<sub>I</sub>, R<sub>I</sub> & R<sub>0</sub>.

- Estimate  $A_V$ ,  $A_I$ ,  $R_I$  &  $R_O$  in an Emitter Follower circuit with  $R_E = 1K$ , b)  $h_{ie} = 1100\Omega$ ,  $h_{fe} = 50$ ,  $h_{re} = 2.4 \times 10^{-4}$ ,  $h_{oe} = 25 \ \mu \text{A/V}$ . [7+8]

- 6.a) With neat sketches, necessary equations explain the drain & transfer characteristics of MOSFET in enhancement mode.

- Why is a Field Effect Transistor called unipolar & voltage controlled device? b) Explain the drain & transfer characteristics of a JFET in detail. [7+8]

- i) Give symbol of UJT and mark required polarities for operation. 7.a) ii) Explain how the UJT can be used as a negative-resistance device with the aid of static characteristics.

- A Common Drain FET amplifier circuit shown in Figure.1 has the following b) circuit parameters:  $R_S = 0.5K$ , Rg = 1M,  $r_d = 5K$ ,  $g_m = 5mS$  and  $V_{DD} = 20 V.$ Calculate A<sub>V</sub> & R<sub>O</sub>. [8+7]

- 8.a) Draw the structure and two-transistor model of SCR, explain its operation with help of V-I characteristics.

- b) Explain the operation of varactor diode with the help of neat diagrams. [10+5]

\*\*\*\*\*\*\* ORI

www.jntuworld.com // www.android.jntuworld.com // www.jwjobs.net // www.android.jwjobs.net

|                 | N 00 4 20202                                                                                                                                                      |            |     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|

|                 | No: 09A30203                                                                                                                                                      |            |     |

| JA              | WAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY, HYDERABAD<br>B. Tech. II Year I Semester Examinations, May/June-2013                                                     |            |     |

|                 | Electronic Devices and Circuits                                                                                                                                   |            |     |

|                 | (Common to EEE, ECE, CSE, EIE, BME, IT, MCT, ETM, ECOMPE, ICE)                                                                                                    |            |     |

| Time:           | 3 hours Co Co Co Max. Marks: 75                                                                                                                                   | 0.0        | Q   |

|                 | Answer any five questions                                                                                                                                         |            |     |

|                 | All questions carry equal marks                                                                                                                                   | 60         | GIL |

|                 |                                                                                                                                                                   | C6         | Q   |

| 1.a)            | Draw the V-I characteristics of a diode with zero cut-in voltage and equivalent                                                                                   |            |     |

| Q6              | resistance of 100 $\Omega$ . Draw the load line if R <sub>L</sub> is also 100 $\Omega$ .                                                                          | <b>C</b> 6 |     |

| b)              | Draw the equivalent circuit of a diode circuit when a DC voltage to forward bias                                                                                  |            |     |

|                 | the diode along with an ac signal is applied.                                                                                                                     |            |     |

| c)              | Differentiate between normal PN junction diode and a Zener diode. [15]                                                                                            |            |     |

| QG              |                                                                                                                                                                   |            |     |

| 2.a)            | Derive expressions for ripple factor, regulation and rectification efficiency of a                                                                                |            |     |

|                 | half wave rectifier. 08 08 08 08 08 08 08                                                                                                                         |            |     |

| b)              | Design an LC filter for a Full wave rectifier to give 9V output as DC voltage at $100 \text{ mA}$ surrent. Assume ring a factor to be $20/$                       |            |     |

| <b>Q6</b><br>c) | 100 mA current. Assume ripple factor to be 2%.<br>Compare the filtering characteristics of capacitance type, choke input type and                                 |            |     |

| 06              | Π-type filters. (15)                                                                                                                                              |            |     |

|                 | In type inters.                                                                                                                                                   |            |     |

| 3.a)            | Based on the currents flowing through a BJT illustrate the amplification process.                                                                                 |            |     |

| b)              | Sketch the input and output characteristics of a BJT in CE configuration and                                                                                      |            |     |

| Q6              | discuss how $\beta$ of the transistor can be determined form the characteristics.                                                                                 |            |     |

| c)              | Compare CB, CC, and CE configurations. [15]                                                                                                                       |            |     |

|                 | ଇଟି ଭାଇ                                                                                                                       |            |     |

| 4.a)            | What is the need of biasing a BJT for amplifier application? List the deficiencies                                                                                |            |     |

|                 | of fixed bias and emitter feedback bias methods and explain how they are                                                                                          |            |     |

| 1.)             | overcome in voltage divider bias method.                                                                                                                          |            |     |

| b)              | Define stability factors for a BJT with any biasing method. Suggest a method to compensate for temperature variation effects on operating point of a BJT circuit. |            |     |

| c)              | What is thermal runaway? Discuss the causes for it. [15]                                                                                                          |            |     |

|                 | what is the man rundway. Discuss the causes for it.                                                                                                               |            |     |

| 5.a)            | Discuss the effect of $V_{GS}$ on drain current of a JFET based on its structure.                                                                                 |            |     |

| b)              | Define: Pinch-off voltage, mutual conductance $(g_m)$ , dynamic drain resistance $(r_d)$                                                                          |            |     |

| 06              | and amplification factor ( $\mu$ ) for a JFET and establish a relation between them.                                                                              |            |     |

| c)              | Explain the operation of a MOSFET in enhancement and depletion modes.                                                                                             |            |     |

|                 | [15]                                                                                                                                                              |            |     |

|                 |                                                                                                                                                                   |            |     |

| 6.a)            | What is the difference between approximate and accurate h-parameter models of a                                                                                   |            |     |

| 1.)             | BJT in CE configuration? Discuss the conditions applicable for each model.                                                                                        |            |     |

| b)              | Draw the h-parameter equivalent circuit of a generalized BJT amplifier and derive expressions for $A = A_1$ , $B_1$ and $B_2$                                     |            |     |

|                 | expressions for $A_v$ , $A_i$ , $R_i$ and $R_o$ . [15]                                                                                                            |            |     |

| 7.a)            | Draw the circuit diagram, equivalent circuit of a JFET small signal amplifier in                                                                                  |            |     |

| ,)              | CS configuration and derive expressions for $A_v$ , $A_i$ , $R_i$ and $R_o$ . Make applicable                                                                     |            |     |

|                 | assumptions and comments.                                                                                                                                         |            |     |

|                 |                                                                                                                                                                   |            |     |

www.jntuworld.com // www.jwjobs.net

In a full-wave rectifier with capacitor filter, show that the ripple voltage is 2.a) inversely proportional to the capacitance of the capacitor and is proportional to the load current. Calculate the ripple voltage, when C = 100 µF and  $I_{DC} = 10 \text{mA}$ . 0e The ac input voltage to the rectifier is Vm sin 314t.

0e

1.16s

ŀ,

÷.

· · ·

- Draw the circuit of Zener voltage regulator. Explain its operation with neat b) characteristics and also derive expressions for minimum and maximum values of source resistor for the Zener diode to work as a voltage regulator.

- Explain Early effect and its consequences in a BJT. Also draw the Ebers-Moll ,3;a) model of a PNP transistor.

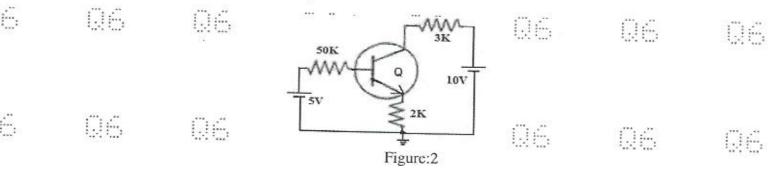

- In the circuit shown in Figure.2, a silicon transistor with  $\beta = 100$ ,  $V_{BE} = 0.7V$  and b)  $V_{CEsat} = 0.2V$  is used. Determine whether the transistor is operated in active region or in saturation region?

- With neat diagram and necessary equations, explain how the variations in V<sub>BE</sub> compensated with the variations in temperature.

- b) Design a self bias circuit using silicon transistor to achieve a stability factor of 10, with the following specifications:  $V_{CC} = 16V$ ;  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA and  $\beta = 50$ .

l. in

1.JE

L. E.

U.

L.F.

1.) 斤,

1.J.÷.,

- 5. a) With neat diagrams and necessary equations, explain the effect of coupling capacitor and bypass capacitor on the performance of an amplifier at low-frequencies?

- The frequencies? In a single stage CE amplifier circuit with unbypassed emitter resistor,  $R_{c.=}$  10K,  $R_E = 1K$  and  $R_S = 0.5K$ . The h-parameters of the transistor used are  $h_{ic} = 1.1K$ ,  $h_{fe} = 50$ ,  $h_{oe} = 25 \ \mu \text{A/V} \& h_{re} = 2.5 \times 10^{-4}$ . Find  $R_i$  and  $A_V$ .

6. a) Draw the basic structure and circuit arrangement of a P-channel Metal Oxide Semiconductor Field Effect Transistor in enhancement mode. Explain the drain and transfer characteristics.

Explain the procedure to obtain the small-signal equivalent circuit of a field effect transistor with necessary equations. Also draw the small-signal model.

7.a) What are the requirements of FET biasing? Verify these requirements in source self-bias circuit.

b) A Common Source FET amplifier circuit shown in Figure 3 with unbypassed Rs has the following circuit parameters: Rd = 15K, Rs = 2.5K, Rg = 1M, rd = 100K, IDSS = 10mA, VP = -5Vand VDD = 20 V. Calculate gm & Av. [7+8]

8.a) Draw the structure and two-transistor model of SCR, explain various methods of triggering an SCR.

With neat sketches, explain the principle of operation of Schottky Barrier Diode.

U6

L.E.

l., i--.

0.

1.J.

\*\*\*\*\*\*\*

Q6

L.F.

÷....

Qé.

l.Jŕn

06

L.E.

in.

÷.

é.

in.

i.

in,

In a full-wave rectifier with capacitor filter, show that the ripple voltage is 2.a) inversely proportional to the capacitance of the capacitor and is proportional to the load current. Calculate the ripple voltage, when C = 100 µF and  $I_{DC} = 10 \text{mA}$ . 0e The ac input voltage to the rectifier is Vm sin 314t.

0e

1.16s

ŀ,

÷.

· · ·

- Draw the circuit of Zener voltage regulator. Explain its operation with neat b) characteristics and also derive expressions for minimum and maximum values of source resistor for the Zener diode to work as a voltage regulator.

- Explain Early effect and its consequences in a BJT. Also draw the Ebers-Moll ,3;a) model of a PNP transistor.

- In the circuit shown in Figure.2, a silicon transistor with  $\beta = 100$ ,  $V_{BE} = 0.7V$  and b)  $V_{CEsat} = 0.2V$  is used. Determine whether the transistor is operated in active region or in saturation region?

- With neat diagram and necessary equations, explain how the variations in V<sub>BE</sub> compensated with the variations in temperature.

- b) Design a self bias circuit using silicon transistor to achieve a stability factor of 10, with the following specifications:  $V_{CC} = 16V$ ;  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA and  $\beta = 50$ .

l. in

1.J.E.

L. E.

U.

1.I÷,

1.) 斤,

1.J.÷.,

- 5. a) With neat diagrams and necessary equations, explain the effect of coupling capacitor and bypass capacitor on the performance of an amplifier at low-frequencies?

- The frequencies? In a single stage CE amplifier circuit with unbypassed emitter resistor,  $R_{c.=}$  10K,  $R_E = 1K$  and  $R_S = 0.5K$ . The h-parameters of the transistor used are  $h_{ic} = 1.1K$ ,  $h_{fe} = 50$ ,  $h_{oe} = 25 \ \mu \text{A/V} \& h_{re} = 2.5 \times 10^{-4}$ . Find  $R_i$  and  $A_V$ .

6. a) Draw the basic structure and circuit arrangement of a P-channel Metal Oxide Semiconductor Field Effect Transistor in enhancement mode. Explain the drain and transfer characteristics.

Explain the procedure to obtain the small-signal equivalent circuit of a field effect transistor with necessary equations. Also draw the small-signal model.

7.a) What are the requirements of FET biasing? Verify these requirements in source self-bias circuit.

b) A Common Source FET amplifier circuit shown in Figure 3 with unbypassed Rs has the following circuit parameters: Rd = 15K, Rs = 2.5K, Rg = 1M, rd = 100K, IDSS = 10mA, VP = -5Vand VDD = 20 V. Calculate gm & Av. [7+8]

8.a) Draw the structure and two-transistor model of SCR, explain various methods of triggering an SCR.

With neat sketches, explain the principle of operation of Schottky Barrier Diode.

U6

L.E.

l., i--.

06

1.J.

\*\*\*\*\*\*\*

Q6

L.F.

÷....

Qé.

l.Jŕn

06

L.E.

in.

÷.

é.

in.

i.

in,

| Code No:A109210203   |   |

|----------------------|---|

| Couc 110./110/210205 | L |

Max. Marks: 75

### B.Tech II Year I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

# Time: 3 hours

#### Answer any five questions All questions carry equal marks

- 1.a) Explain the concept of diode capacitance. Derive expression for transition capacitance?

- b) Find the value of D.C. resistance and A.C resistance of a Germanium junction diode at  $25^{\circ}$  C with reverse saturation current,  $I_{o} = 25\mu$ A and at an applied voltage of 0.2V across the diode. [8+7]

- Define the following terms and derive the equations with respect to half-wave rectifier:

i) Ripple factor

ii) Rectification efficiency

iv) % Regulation.

- 3.a) With neat sketches and necessary waveforms, explain the input and output characteristics of a BJT in CB configuration. Also derive expression for output current.

- b) Derive the relation among  $\alpha$ ,  $\beta$  and  $\gamma$ .

- 4.a) Explain the basic requirements of transistor biasing. Verify these requirements in collector to base bias circuit.

- b) Design a fixed bias circuit using silicon transistor, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [8+7]

- Draw the circuit diagram, AC equivalent & small signal equivalent of Common Base amplifier using accurate h-parameter model. Derive expressions for A<sub>Vs</sub>, A<sub>Is</sub>, R<sub>I</sub> & R<sub>0</sub>. [15]

- 6.a) Explain the construction & operation of an N-channel enhancement and depletion MOSFET with the help of static drain characteristics and transfer characteristics.

- b) Define pinch-off voltage and transconductance in field effect transistors. [12+3]

- 7.a) Draw the small-signal model of common drain FET amplifier. Derive expressions for voltage gain and output resistance.

- b) Calculate voltage gain  $A_V = V_O/V_i$  and  $R_O$  at 1KHz for the circuit shown in Figure 1. FET parameters are gm=2mA/V and rd =10k. Neglect capacitances.

[8+7]

[10+5]

8. With neat energy band diagrams, explain the V-I characteristics of Tunnel diode in detail. Also explain the negative-resistance region in the characteristics and applications of Tunnel diode. [15]

# B.Tech II Year - I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

### Time: 3 hours

Max. Marks: 75

#### Answer any five questions All questions carry equal marks

- 1.a) What do you understand by depletion region at p-n junction? What is the effect of forward and reverse biasing of p-n junction on the depletion region? Explain with necessary diagrams.

- b) Explain Zener and avalanche breakdown mechanisms in detail. [8+7]

- 2.a) Draw the circuit diagram of full-wave rectifier with inductor filter. Explain its operation with necessary equations.

- b) A HWR circuit supplies 100mA DC current to a  $250\Omega$  load. Find the DC output voltage, PIV rating of a diode and the r.m.s. voltage for the transformer supplying the rectifier. [8+7]

- 3.a) With neat sketches and necessary waveforms, explain the input and output characteristics of a BJT in CE configuration. Also derive expression for output current.

- b) Calculate the collector current and emitter current for a transistor with  $\alpha = 0.99$ and  $I_{CBO} = 50\mu A$  when the base current is 20 $\mu A$ . [10+5]

- 4.a) What is thermal runaway in transistors? Obtain the condition for thermal stability in transistors.

- b) Design a self bias circuit using silicon transistor to achieve a stability factor of 10, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [6+9]

- Draw the circuit diagram, AC equivalent & small signal equivalent of Emitter Follower amplifier using accurate h-parameter model. Derive expressions for A<sub>Vs</sub>, A<sub>Is</sub>, R<sub>I</sub> & R<sub>0</sub>. [15]

- 6.a) With the help of neat sketches and characteristic curves explain the construction & operation of a JFET and mark the regions of operation on the characteristics.

- b) Derive expression for transconductance in a field effect transistor. [10+5]

- 7.a) Draw the small-signal model of common source FET amplifier. Derive expressions for voltage gain and output resistance.

- b) Give the UJT symbol and simplified equivalent circuit with external resistors included. Describe its negative-resistance nature, with the help of V-I characteristics. [7+8]

- 8.a) With neat sketches, explain the principle of operation of Schottky Barrier Diode.

- b) With neat sketches, explain V-I characteristics of semiconductor Photo Diode.

[8+7]

\*\*\*\*\*\*\*

Max. Marks: 75

# B.Tech II Year - I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

# Time: 3 hours

#### Answer any five questions All questions carry equal marks

- 1.a) Explain about various current components in a forward biased p-n junction diode.

- b) With neat sketches and necessary waveforms explain about the regulation characteristics of Zener diode. [7+8]

- 2.a) Draw the circuit of full-wave rectifier with capacitor filter. Explain its operation with necessary equations.

- b) A full wave rectifier circuit uses two silicon diodes with a forward resistance of  $20\Omega$  each. A DC voltmeter connected across the load of  $1K\Omega$  reads 55.4 volts. Calculate

| i) I <sub>rms</sub> | ii) Average voltage across each diode     |       |

|---------------------|-------------------------------------------|-------|

| iii) ripple factor  | iv) Transformer secondary voltage rating. | [7+8] |

- 3.a) With neat sketches and necessary waveforms, explain the input and output characteristics of a BJT in CE configuration. Also derive expression for output current.

- b) The reverse leakage current of the transistor when connected in CB configuration is 0.2  $\mu$ A while it is 18  $\mu$ A when the same transistor is connected in CE configuration. Calculate  $\alpha$  and  $\beta$  of the transistor. [10+5]

- 4.a) Explain how I<sub>CO</sub> variations are compensated with the help of diode and thermistor in transistor biasing circuits?

- b) Design a collector to base bias circuit using silicon transistor to achieve a stability factor of 20, with the following specifications:  $V_{CC} = 16V$ ,  $V_{BE} = 0.7V$ ,  $V_{CEQ} = 8V$ ,  $I_{CQ} = 4$  mA &  $\beta = 50$ . [7+8]

- 5. Draw the basic circuit, ac equivalent and h-parameter model of a Common Emitter amplifier. Derive expressions for  $A_{Vs}$ ,  $A_{Is}$ ,  $R_I \& R_O$ . [15]

- 6.a) Explain the construction & operation of an P-channel enhancement and depletion MOSFET with the help of static drain characteristics and transfer characteristics.

- b) Explain why field effect transistor is called as unipolar and voltage controlled device. [12+3]

- 7.a) Draw the small-signal model of common gate FET amplifier. Derive expressions for voltage gain and input resistance.

- b) A Common Source FET amplifier circuit shown in Figure.1 with unbypassed  $R_s$  has the following circuit parameters:  $R_d = 15K$ ,  $R_S = 0.5K$ , Rg = 1M,  $r_d = 5K$ ,  $g_m = 5mS$  and  $V_{DD} = 20$  V. Calculate  $A_V \& R_O$ . [8+7]

8. With neat energy band diagrams, explain the V-I characteristics of Tunnel diode in detail. Also explain the negative-resistance region in the characteristics. [15]

| Code No:A109210203 |  |

|--------------------|--|

| COUE NO.A109210203 |  |

#### B.Tech II Year - I Semester Examinations, May-June, 2012 ELECTRONIC DEVICES AND CIRCUITS

(COMMON TO BME, CSE, EEE, ECE, ECC, EIE, ETM, IT, ICE, MCT)

Time: 3 hours

Max. Marks: 75

[8+4+3]

#### Answer any five questions All questions carry equal marks

- 1.a) With neat sketches and necessary waveforms explain the volt ampere characteristics of PN diode.

- b) Explain the temperature dependence of VI characteristics of PN diode.

- c) Compare ideal and practical diodes.

- 2.a) Draw the circuit of full-wave rectifier with L-section filter and derive expression for its ripple factor.

- b) A 230 V, 60Hz voltage is applied to the primary of a 5:1 step down, center tapped transformer used in a full wave rectifier having a load of 900 $\Omega$ . If the diode resistance and the secondary coil resistance together has a resistance of 100 $\Omega$ , determine

i) dc voltage across the load.iii) dc power delivered to the load.

- ii) dc current flowing through the load.

- iv) PIV across each diode. [7+8]

- 3.a) With the help of a neat diagram explain different current components in an NPN bipolar junction transistor.

- b) With reference to bipolar junction transistors, define the following terms and explain.

- i) Emitter efficiency.

ii) Base Transportation factor.

iii) Large signal current gain.

[9+6]

- 4.a) Explain the basic requirements of transistor biasing. Verify these requirements in Emitter feedback bias circuit.

- b) An NPN Silicon transistor with  $\beta$ =50 is used in a common emitter circuit with V<sub>CC</sub>=10V, R<sub>C</sub>=2K. The bias is obtained by connecting a 100K resistance from collector to base. Find i) Q-Point ii) Stability factor, S [8+7]

- 5.a) Compare CB, CE and CC amplifiers in view of A<sub>V</sub>, A<sub>I</sub>, R<sub>I</sub> & R<sub>O</sub>.

- b) Estimate  $A_V$ ,  $A_I$ ,  $R_I$  &  $R_O$  in an Emitter Follower circuit with  $R_E = 1K$ ,  $h_{ie} = 1100\Omega$ ,  $h_{fe} = 50$ ,  $h_{re} = 2.4 \times 10^{-4}$ ,  $h_{oe} = 25 \,\mu A/V$ . [7+8]

- 6.a) With neat sketches, necessary equations explain the drain & transfer characteristics of MOSFET in enhancement mode.

- b) Why is a Field Effect Transistor called unipolar & voltage controlled device? Explain the drain & transfer characteristics of a JFET in detail. [7+8]

- 7.a) i) Give symbol of UJT and mark required polarities for operation.ii) Explain how the UJT can be used as a negative-resistance device with the aid of static characteristics.

- b) A Common Drain FET amplifier circuit shown in Figure.1 has the following circuit parameters:  $R_S = 0.5K$ , Rg = 1M,  $r_d = 5K$ ,  $g_m = 5mS$  and  $V_{DD} = 20$  V. Calculate  $A_V \& R_O$ . [8+7]

- 8.a) Draw the structure and two-transistor model of SCR, explain its operation with help of V-I characteristics.

- b) Explain the operation of varactor diode with the help of neat diagrams. [10+5]

\*\*\*\*\*\*\* ORI